基于ARM+FPGA的ISA总线/MMи总线接口转换设计在轨道交通的应用

作者:小教学发布时间:2023-10-02分类:程序开发学习浏览:272

总线广泛应用于计算机、工业生产及各种测试设备。ISA总线为IBM公司推出的基于80286CPU的PC/AT微型计算机用扩展总线标准,MMи总线是俄罗斯国内自行设计的专用测试总线,主要用于程控单元模块与MMи总线之间数据及控制信息的交换。在某型导弹测试设备中,工控计算机采用了ISA总线,而俄制测试设备采用了MMи总线,2种总线数据模式和传输制式不同。本文以FPGA为核心,设计了ISA总线/MMи总线2种总线之间的数据和控制指令转换电路,实际应用证明了该电路的可靠性。

1 ISA总线和MMи总线简介

1.1 ISA总线

ISA(Industrial Standard Architecture)总线是IBM公司于1984年进一步扩充XT总线标准而形成的。ISA总线标准支持24位的地址线、16位的数据线;支持11级中断IRQ3~IRQ7,IRQ9~IRQ12,IRQ14~IRQ15;支持7个DMA传输通道DRQ0~DRQ3,DRQ5~DRQ7;支持主从控制、I/O等待和I/O校验等功能。为了与XT总线保持向下兼容,ISA总线在信号功能的定义和物理接口上均作了特殊的安排,即保持原有的XT总线不变,重新增加一个36线的连接插槽,分成C,D两面,扩充的功能设计在C,D两面的信号线上。其引脚定义如下:

(1)数据总线SD0~SD7。SD0~SD7为8位双向三态数据总线,在芯片和主接口间传输命令、数据和状态。SD7为最高位。

寄存器选择引脚为SA4~SA9,SW DIP-6(板基址011001)和。这些引脚决定转换是否响应I/O周期,当为逻辑低电平且SA4~SA9与6位拨动开关值完全匹配时,内部产生一个片选信号,使转换响应I/O周期。

(2)地址信号SA0~SA3。I/O读写操作时作为转换电路上FPGA芯片内的寄存器选择信号。

(3)读写信号,。写操作中,转换在上升沿锁存数据。读操作中,当有效时,转换模块直接驱动8位数据线。

(4)中断信号INTR。中断状态寄存器某使能中断为真时,INTR有效。对INTR的有效声明没有最小脉宽要求。

(5)I/O通道准备好信号IO CHRDY。IOCHRDY变低,表明当前I/O周期需要被延长。写周期中,当数据从ISA总线上被锁存时IO CHRDY变高。读周期中,数据有效时IO CHRDY变高。进行寄存器读写时IO CHRDY被拉低。IO CHRDY引脚用集电极开路逻辑门驱动,因此此信号会由一个内部上拉电阻上拉至逻辑高电平。

(6)复位信号RESET。RESET信号有效时,触发转换模块,使FPGA硬重肩。

1.2 MMи总线

MMи总线是俄罗斯国内自行设计的专用测试总线,主要用于程控单元模块与MMи总线之间数字及控制信息的交换,其基本技术性能如下:

(1)MMи总线采用异步、字节串行、位并行、双向信息传输方式。

(2)MMи总线采用负逻辑,模块服务请求信号(зOм)和转换结束信号(KПp)除外。低电平电压为0~0.6 V,表示逻辑1(对于服务请求信号зOМ和转换结束信号KПp,逻辑1的电平为2.4~4.5 V);高电平电压为2.4~4.5 V,表示逻辑0(对于服务请求信号зOМ和转换结束信号KПp,逻辑0的电平为0~0.6 V)。

(3)总线上挂接的程控单元模块最多为16个(包括控制器)。

(4)MMи总线中最多包含92根信号线路。一个程控单元模块内所使用的线路最多不超过50根,最少不少于15根。每一个具体的程控单元模块所用的线路数量,可根据此模块的具体技术要求确定。

(5)程控单元模块与MMи控制器间总线电缆的最大长度不应超过1 m。

(6)总线内的信息传输最大速度由程控单元模块与MMи总线的信息处理能力决定,最大不超过100 Kb/s。

(7)总线控制器与程控单元模块间的连接方式有2种:链型连接及星型连接。链型连接总线上的所有装置,包括控制器,都是并行连接的;其中的信号可以单向或双向传输;星型连接总线将MMи控制器与单个程控单元模块一对一地连接到一起,其中的信号单向传输。

(8)MMи总线线路可分以下6类:

数据线:“1 pиM,….8 pиM”线路(数据总线);第1电平地址线——“Aдp.эм”线路(程控模块单元地址);第2电平地址线——“A0…A15”线路(信息寄存器地址);同步线——“ΓT”(准备好),“Пpиeм”(接收),“Bыд”(发送),“Kнп”(传输结束)线路;控制线——“иAэм”(初始化),“эaпycK эм”(触发),“ПOзм”(串行询问),“KOм.1……KOм.16”(控制指令)线路;中断线——“зOм”(请求服务),“Kпp”(转换结束)线路。

程控单元模块从MMи控制器接收的所有指令都是寻址指令。在中断线内,模块服务请求信号“зOм”具有高优先级,转换结束信号“Kпp”具有低优先级。

2 硬件设计

2.1 工作原理

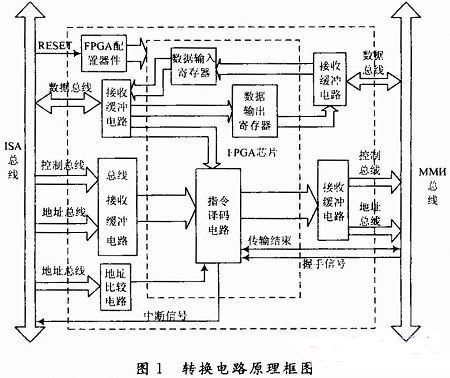

如图1所示,转换电路由FPGA芯片EPF10K30-RI208-4、FPGA配置器件EPC2LI20、接收缓冲电路、地址比较电路和总线接收电路组成。工作原理如下:当转换电路工作时,首先根据FPGA配置器件内的文件对FPGA芯片进行自动配置,当ISA总线相应地址位与6位拨动开关值匹配时(拨动开关为预设待转数据模块地址),选中需要转换数据的地址,然后由ISA数据总线发送数据或命令,FPGA芯片中的译码电路结合地址总线信号和控制总线信号将控制数据转为MMи总线对后级程控模块的控制指令,对后级模块实现控制。

当传递某MMи程控模块的数据时,首先将MMи程控模块初始化,然后由ISA总线发送“模块选址”数据,写入FPGA中地址寄存器后,经译码产生选址信号,并由触发器保持。选址后,ISA总线发送“初始化”指令,写入命令寄存器后,经译码产生初始化信号。当监测到“准备好”信号时,说明初始化成功,发送“清除模块选址”信号。

MMи程控模块接收信息时,在被寻址且发出准备好信号后,ISA总线将要写入程控模块的数据先写入FPGA中的数据输出寄存器中,然后发送到MMи数据总线上,发出“Пpиeм”接收信号,程控模块根据此信号将数据写入相应信息寄存器。信息接收结束后,取消“Пpиeм”接收信号,取消MMи数据总线上数据。程控模块准备接收新的信息字节,并产生准备好的信号。

程控模块发送信息时,在被寻址且发出准备好信号后,由ISA总线控制沿“A0~A2”线路指定接收信息寄存器地址,并发出“Bыд.”发送信号,程控模块根据此信号从发送信息寄存器沿MMи数据总线发出信息字节,所发出的信息字节被读取到FPGA中的数据输入寄存器后由ISA总线控制读出。

2.2 FPGA配置器件电路

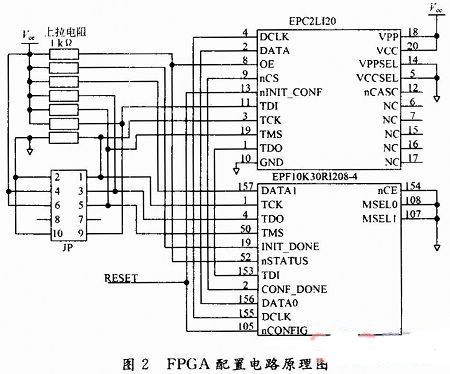

FPGA配置器件电路如图2所示,EPC2LI20为配置芯片,工作电压5 V或3.3 V,支持在系统编程(ISP)和菊花链配置,可重复编程;EPF10K 30R1208-4为Altera公司生产FPGA芯片,工作电压为5 V,包含逻辑单元1 728个,存储位数12 288位;JP为通过QuartusⅡ软件对配置芯片进行程序烧写接口。

该配置电路采用PS配置方式,首先通过QuartusⅡ软件将FPGA的逻辑程序写入配置芯片EPC2LI20,该芯片数据具有掉电保护功能。上电后,配置芯片和FPGA同时复位,然后FPGA向配置芯片发送程序下载请求,配置芯片将存储的逻辑程序写入FPGA,对FPGA进行配置.配置完成后,FPGA内部的寄存器和I/O管脚均被初始化。完成初始化程序后,FPGA按照设计的逻辑功能正常工作,即按要求实现两种总线之间的数据转换。

2.3 地址比较电路

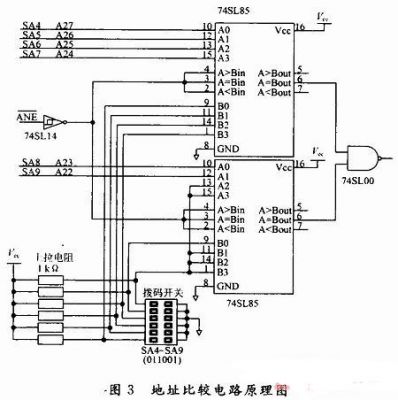

地址比较电路如图3所示。74SL14为带滞环比较的反向缓冲器,74SL85为4位数字比较器,6位的拨码开关为预存待转数据程控模块地址,74SL00为反向缓冲器。拨码开关共有6位,每1位都可以是逻辑高电平“1”或是逻辑低电平“0”,故该拨码开关共有26个组合,可以代表26个程控模块的地址。如图3所示,拨码开关为011001,代表将要进行转换的数据来自地址为011001的程控模块,当控制信号给定的地址A27~A22与011001相符时,74SL00输出低电平,该低电平与ISA总线的读控制信号IOR和写控制信号IOW#一起构成FPGA从ISA总线读数据或向ISA总线写数据控制信号。

3 程序设计

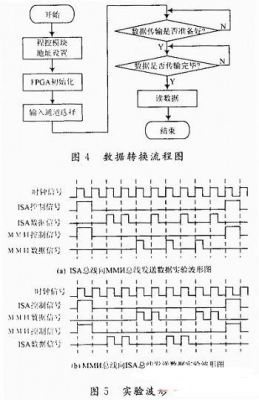

实现ISA总线/MMи总线之间的数据转换流程图如图4所示。程序开始后,首先与拨码开关比较得到待转换数据程控模块的地址,然后FPGA通过配置芯片进行初始化,初始化完成后,待转数据程控模块的地址写入FPGA,FPGA自动分配传输数据的通道;然后,由ISA总线(MMи总线)发出数据传输请求信号,当MMи总线(ISA总线)准备好接收数据后,发一个应答信号给ISA总线(MMи总线),表示数据传输准备好,然后进行数据传输,一直到数据传输完毕;发送的数据写入接收端的数据缓冲器,MMи总线(ISA总线)从数据缓冲器读出输出的数据发送到相应的程控模块,从而完成从ISA总线(MMи总线)到MMи总线(ISA总线)的数据转换。

4 实验结果

应用设计的ISA总线/MMи总线转换电路以串行方式对一组数据进行转换。ISA总线向MMи总线传输数据的实验结果如图5(a)所示,当ISA控制信号发出询问脉冲(第2个波形第1个脉冲)时,MMи总线给出应答信号(第4个波形第1个脉冲);收到MMи总线给出的应答(同步)信号后,ISA总线将数据信号11010101发送(第3个波形);由于MMи总线数据信号采用的是负逻辑,因此,MMи总线上收到了发送的信号00101010(第5个波形)。实验结果证明,设计的电路可以实现ISA总线到MMи总线的数据转换。由MMи总线向ISA总线传输数据的实验结果如图5(b)所示,当MMи总线发送的数据为00110011时,ISA总线接收的数据为11001100。

用设计的电路插板更换导弹测试设备上的俄制电路插板,并用测试设备对某型导弹进行常规测试,测试结果符合测试要求。实际应用证明,设计的电路达到设计目的,可以可靠地实现ISA总线/MMи总线之间的数据转换。

5 结语

ISA总线和MMи总线是2种完全不同的总线,ISA总线采用美制标准,而MMи总线采用俄制标准,因此在俄制测试设备中,ISA总线/MMи总线的转换电路板是必备的。本文设计的电路完全能代替俄制电路板实现数据转换功能,极大提高了部队装备的保障力;同时,由于俄制电路板价格较贵,因此采用国产器件实现的该转换电路也具有较高的经济价值。

- 程序开发学习排行

- 最近发表