数字IC/FPGA面试宝典--经典60道例题详解

作者:小教学发布时间:2023-09-26分类:程序开发学习浏览:275

1.关于亚稳态的描述错误的是(A)

A、多用几级寄存器打拍可以消除亚稳态。

B、亚稳态是极不稳定的,理论上来讲处在亚稳态的时间可以无限长。

C、亚稳态稳定到0或者1,是随机的,与输入没有必然的关系。

D、如果数据传输中不满足触发器的建文时间Tsu和保持时间Th,可能产生亚稳态。

解析:亚稳态无法消除,只能尽量避免。

2.下列关于综合的说法哪项是不正确的(B)

A.综合(Synthesis)简单地说就是将HDL代码转化为门级网表的过程

B.综合由Translation和Mapping两个步骤组成

C.Mapping把用GTECH库元件构成的电路映射到某一特定厂家的工艺库上

D.Translation是指把HDL语言描述的电路转化为用GTECH库元件组成的逻辑电路的过程

解析:

综合,就是将概念转换为可制造器件的转移过程。

综合是将RTL转换成门级网表(gate-level netlist)的过程。综合过程分为转换(translation),优化(optimization)、映射(mapping)。

综合工具先通过read命令将RTL代码转化成通用的布尔等式,即GTECH(generic technology)。然后执行compile命令,根据设计者施加的延时,面积等约束,对网表进行优化。最后将RTL网表映射到工艺库上,成为一个门级网表。门级网表输入到布局布线工具,由它产生GDSll文件,验证正确后,交付芯片生产商制造。

综合以时序路径为基础进行优化。DC在对设计做综合时,其过程包括了进行静态时序分析(static timing analysis STA)。DC使用内建的时序分析器把设计分解成多条时间路径,然后根据设计的约束对路径进行优化。如果某条路径的延时大于约束的值,则时序违例。也可以用Prime Time作静态时序分析。PT是独立的时序分析器,主要用于整个芯片门级电路的静态时序分析。

Translation:将RTL描述转换成未优化的门级布尔描述,包括相应的功能块以及功能块之间的拓扑结构。

Optimization:根据所施加的时序和面积约束,按照一定的算法对翻译结果进行逻辑重组和优化。Mapping:根据所施加的时序和面积约束,从目标工艺库中搜索符合条件的单元来构成实际电路的逻辑网表。

(SV验证)3.当功能覆盖率(Functional Coverage)达到100%,可以说明:(C)

A.DUT的功能点已经100%覆盖。

B.功能覆盖率(FunctionalCoverage)对应的DUT响应是正确的。

C.某些令人关注的情况已经得到测试覆盖。

D.验证工作可以结束

测试点是人为分解得出的,无法保证100%覆盖,也无法保证100%正确,只能说明某些关注的情况得到覆盖,功能点都没有覆盖,验证工作怎么可以结束。即使代码覆盖率和功能覆盖率都达到100%,也要怀有对芯片流片的敬畏之心。

System Verilog:覆盖率 2 个大方面:代码覆盖率,功能覆盖率。

代码覆盖率主要包括:

(1)分支覆盖率;

针对 if…else、case 等分支语句,看代码中设计的分支是否都被测试到了。

针对 if(条件1),只要条件 1 取 true 和 false 都执行过,则这个分支就完全覆盖了。

(2)语句覆盖率

语句覆盖率上不去时,可以查看未覆盖处的代码是测试用例的疏忽、冗余代码或是保护用途的代码,比如case的default(如果出现此类,一般是case的条件已经全部列出,可以将最后一个条件改为default)。

(3)翻转覆盖率

包括两态翻转(0/1)和三态翻转(0/1/Z),常用的是两态翻转。对于单比特信号而言,若仿真用例使得该信号从0到1和从1到0的翻转均发生,则认为这里的翻转覆盖率是全面的(100%)。

即使翻转覆盖率达到 100%,分支覆盖率和语句覆盖率也不一定达到 100%。

(4)条件覆盖率;

条件覆盖率可以看作是对分支覆盖率的补充。每一个分支条件表达式中,所有条件的覆盖。

(5)状态机覆盖率;

状态机覆盖率主要检查当前状态到下一个状态的跳转是否都跳转过。

功能覆盖率:

又称黑盒测试覆盖率,只关心功能,不关心具体的代码是如何实现的。如果想要统计功能覆盖率,需要在 SystemVerilog 编写的测试用例中添加覆盖组(需要根据功能写测试变量的覆盖率,工具按照覆盖率统计覆盖率),仿真器基于它来统计功能覆盖率。

实现方式主要分为覆盖点(coverage points)和断言(arrertion)。

4.使用相同时钟沿的同步数字电路,以下因素和最高工作频率无关的是:(C)

A.触发器之间最长的组合逻辑

B.触发器的建立/保持时间

C.时钟低电平持续时间

D.逻辑块间互连布线长度

STA: 最高工作频率

对于同步数字电路的最高频率,主要取决于关键路径是否能够收敛,那么就和a,c,d有关系。时钟的低电平持续时间主要影响到时钟信号的有效性。需要做clock pulse width检测,保证该时钟沿能正确地被寄存器采集。如果不满足,则逻辑功能有问题,和最高工作频率无关。

(STA)5,.同步电路设计中出现setup time不满足,不可以采用下面哪种措施解决(A)

A.增加时钟频率

B.减小信号延迟

C.pipeline

D.降低时钟频率

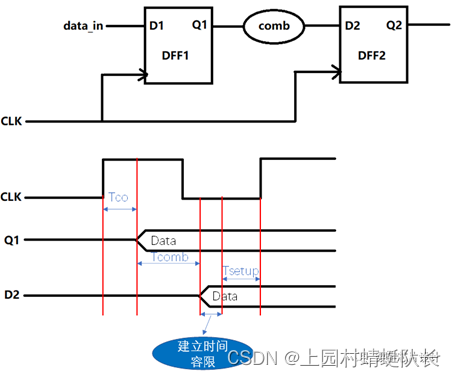

上面就是个同步时序电路。

建立时间为时钟上升沿到来之前输入数据保持稳定的时间。如上图所示,Tco为时钟上升沿到DFF1的输出端Q1的时间间隔,可以理解为触发器DFF1的输出时间延时;Tcomb是组合逻辑电路的传输延时;Tsetup为DFF2的建立时间。即如果要满足DFF2的建立时间,那么建立时间容限必须要大于等于0。

建立时间容限=T(时钟周期)-Tco-Tcomb-Tsetup>=0

A选项,采用流水线(pipeline)结构,在组合逻辑之间插入触发器,Tcomb减小;B选项,减小信号延迟,Tco和Tcomb减小;C选项,降低时钟频率,T增大;以上三种方法都可以增加建立时间容限,可以解决建立时间不满足问题。D选项,增加时钟频率,T减小,会减小建立时间容限,建立时间将会更不满足,所以D错误!

正确答案:D

STA 只适合同步电路

(跨时钟处理)6.下列说法正确的是(C)

A.设计异步FIFO时采用格雷码的原因主要是为了省功耗

B.对单比特控制信号打两拍后可以完全避免了亚稳态

C.异步处理需要考虑发送和接收时钟之间的频率关系

D.尽量将异步逻辑和同步逻辑剥离开,分别在不同的模块中实现

1.使用格雷的唯一目的就是“即使在亚稳态进行读写指针抽样也能进行正确的空满状态判断”

将多 bit 的自然二进制读写地址转成格雷码,相邻数据仅有 1 bit 的不同,可以使用“打两拍”的二级同步器进行读写地址传输;

2. 快到慢就没办法使用“打两拍”;

慢到快的单比特信号打两拍,仅仅是降低了亚稳态发生的概率,但是没有消除亚稳态;

亚稳态无法消除,只能降低发生的概率,二级同步不够的时候可以使用三级甚至四级.

3. 异步处理需要考虑两个时钟的频率,比如前面提到的

| 单bit(慢时钟域到快时钟域): | 快的一定能采到慢的,用快时钟打两拍; |

| 单bit(快时钟域到慢时钟域): | 快时钟域的信号脉宽较窄,慢时钟域不一定能采到,可以通过握手机制让窄脉冲展宽,慢时钟域采集到信号后再“告诉”快时钟域已经采集到信号,确保能采集到; |

(快时钟域到慢时钟域),对单比特控制信号采用双寄存器法打拍无法消除亚稳态

(类似题目)关于亚稳态,以下说法错误的是(B)

A.亚稳态出现的概率与器件工艺,时钟频率等有关系。

B.亚稳态打两拍就可以消除。

C.数字系统中,信号无法满足setup和Hold时容易出现亚稳态。

D.当一个触发器进入亚稳态,既无法准确预测寄存器的输出电平,也很难预测何时输出才能稳定在某个正确的电平上。

(数电基础)7.Moore状态机和Mealy状态机的差异在(C)是否相关。

A.状态和输入信号

B.输出信号和状态

C.输出信号和输入信号

D.状态和输出信号

(计算机体系)8. 计算机执行程序时,在(A)的控制下,逐条从内存中取出指令、分析指令、执行指令。

A.控制器

B.运算器

C.存储器

D.I/o设备

当计算机执行程序时,控制器首先从指令寄存器中取得指令的地址,并将下一条指令的地址存入指令寄存器中,然后从 存储器 中取出指令,由指令译码器对指令进行译码后产生 控制信号 ,用以驱动相应的硬件完成指令操作。

(IC基础)9. 相互间相位固定且频率相同的时钟就是同步时钟。

(同步时钟)数字设计中,一般认为,频率相同或频率比为整数倍、且相位相同或相位差固定的两个时钟为同步时钟。

或者理解为,时钟同源且频率比为整数倍的两个时钟为同步时钟。其实,时钟同源,就保证了时钟相位差的固定性。

(异步时钟)工作在异步时钟下的两个模块进行数据交互时,由于时钟相位关系不可控制,很容易导致建立时间和保持时间 violation。以下 3 种情况下的时钟可以认为是异步的。

◆不同源

由两个不同的时钟源产生的两个时钟是异步的,这是最常见的异步时钟。即便两个时钟频率相同,但是也不能保证每次上电后两者的相位或相位差是相同的,所以信号间的传输与时钟关系也是不确定的。

◆同源但频率比不是整数倍

此时两个时钟间相位差也可能会有多个,例如同源的 7MHz 时钟和 3MHz 时钟,他们之间也会出现多个相位差,时序也难以控制。一般情况下也需要当异步时钟处理。

◆同源虽频率比为整数倍但不满足时序要求。

(验证知识)10.下述关于覆盖率收集结果的描述正确的是(AD)

A.代码覆盖率高、功能覆盖率低,需要加强功能点的覆盖。

B.代码覆盖率低、功能覆盖率高,往往是一个危险信号,说明功能覆盖率建模还不完善

C.功能覆盖率达到100时,代码覆盖率一定已经全部覆盖

D.代码覆盖率高,功能覆盖率高,往往标志验证正处于收敛状态,需要加强各边界点和异常点的测试。

(1)功能覆盖率高但是代码覆盖率低。

分析未覆盖到的代码,推断仿真是否有遗漏的功能点,代码是否为冗余或不可达代码;

(2)功能覆盖率低但是代码覆盖率高

仿真用例没有关注到一些功能点,需要修改测试用例,加强功能点的覆盖。

(变形)高的功能覆盖率意味着高的代码覆盖率(B)

【A】正确

【B】错误

解析:覆盖率包括代码覆盖率、功能覆盖率、漏洞覆盖率、断言覆盖率等。功能覆盖率是和设计意图紧密相连的,有时也被称为“规范覆盖率”,而代码覆盖率则是衡量设计的实现情况。设想某个代码块在设计中被漏掉的情况,代码覆盖率不能发现这个错误,但是功能覆盖率可以。代码覆盖率与功能覆盖率是并列的关系,二者并没有本质的联系。

(数电基础)11.数字电路设计中,下列哪种手段无法消除竞争冒险现象(D)

【A】加滤波电容,消除毛刺

【B】增加冗余项消除逻辑冒险

【C】增加选通信号,避开毛刺

【D】降低时钟频率

解析:数字电路中常见消除竞争与冒险的方法:1、接入滤波电容,因为尖峰脉冲一般都很窄(多在几十纳秒以内),所以只需要在输出端接一个很小的滤波电容,就可以将尖峰脉冲的宽度削弱至电路的阈值电压以下。但输出波形随电容变化,所以适用于对波形前、后沿无严格要求的场合,所以A选项正确;2、引入选通脉冲,选通脉冲在输出稳定之后才拉高,所以可以消除稳定之前的尖峰脉冲。但是,使用这种方法,必须得到一个与输入信号同步的选通脉冲,对它的宽度和作用时间有严格的要求,所以C选项正确;3、修改逻辑设计,增加冗余项。这种方法使用范围有限,考虑的情况比较多,在不同输入的时候,冗余项会不一样,所以如果考虑所有情况,会花费比较多的资源,如果设计的好,适用范围可以适当增加,所以B选项正确;由于在组合逻辑电路中,某个输入变量通过两条或两条以上的途径传到输出端,由于每条途径延迟时间不同,到达输出门的时间就有先有后,这种现象称为竞争,降低时钟频率并不能消除竞争冒险现象,所以D错误。

(SV)12. bit、logic、reg都是4态数据类型(B)

A.正确

B.错误

bit是2值逻辑,4值逻辑为0,1,x,z

(亚稳态)13. 关于亚稳态,以下说法错误的是(B)

A.亚稳态出现的概率与器件工艺,时钟频率等有关系

B.亚稳态打两拍就可以消除

C.数字系统中,信号无法满足setup和Hold时容易出现亚稳态

D.当一个触发器进入亚稳态,既无法准确预测寄存器的输出电平,也很难预测何时输出才能稳定在某个正确的电平上

亚稳态消除不了的。

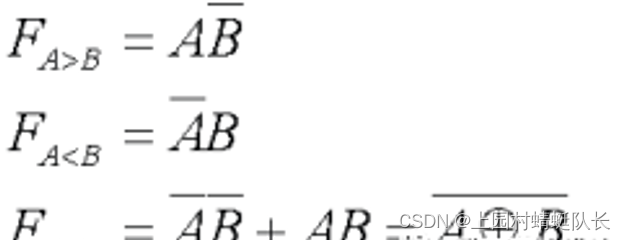

(面积)14. 对于两个位宽相同的无符号数a和b,a>b和a<b两个比较器面积是一样的(A)

A.正确

B.错误

解析:在各种数字系统尤其是在数字电子计算机中,用来完成两个二进制数的大小比较的逻辑电路称为二进制比较器。在数字电路中,二进制比较器的输入是要进行比较的两个二进制数,输出是比较的结果。首先讨论1位数值比较器,1位数值比较器是多位比较器的基础,当A和B都是1位二进制数时,它们的取值和比较结果可由1位数值比较器的真值表表示,由真值表可得如下逻辑表达式:

从上述逻辑,我们可以看出A>B和A<B的逻辑中使用的逻辑关系是对称的。因此,我们可以得到A>B和A<B的面积是相同的。

(面积)15. 对于相同位数输入的变量比较器,大于和小于的面积是一样的 (B)

A.正确

B.错误

无符号数面积相同,有符号数面积不同。

(低功耗)16.以下说法关于低功耗的说法不正确的是:(D)

A.采用合理的powergating方案可以降低功耗。

B.clockgating可以降低芯片功耗

C.通过降低数据的翻转率可以降低功耗。

D.无论设计大小,一律采用先进工艺。

低功耗专题

一道简单的笔试题_低功耗设计 (qq.com)

1.概念

功耗的构成:三个主要的功耗源:浪涌、静态功耗和动态功耗;

浪涌电流:指器件上电时产生的最大瞬时输入电流,称为启动电流;浪涌电流与设备相关; 浪涌功耗不是我们需要关注的地方,因此这里只是说明有这个功耗存在。

静态功耗:也称待机功耗,静态功耗主要由晶体管的漏电流所导致的功耗;

动态功耗:包括开关功耗或者称为翻转功耗、短路功耗或者称为内部功耗。

动态功耗影响因素:门寄生电容、时钟翻转率、时钟频率、供电电压;

降低功耗:应当在所有设计层次上进行,即系统级、逻辑级和物理级,层次越高对功耗降低越有效;在系统和体系结构级可以达到最大的降低效果;

动态功耗是由翻转电流和短路电流引起的功耗。翻转功耗是电路在开关过程中对输出节点的负载电容充放电所消耗的功耗。短路功耗是此时翻转过程中NMOS管和PMOS管同时导通产生短路电流引起的功耗。

静态功耗由漏电流引起的功耗。其中漏电流主要由PN结反向电流、源极和漏极之间的亚阈值漏电流、栅极漏电流和栅极和衬底之间的隧道漏电流组成。

动态功耗可以通过多电压域、预计算、门控时钟等低功耗技术来降低。静态功耗通过多阈值工艺方法、电源门控和体偏置方法来降低。

2.低功耗技术

2.1系统级降低功耗技术:

- 片上系统方法

- 硬件/软件划分:对系统性能进行仿真建模,决定哪一部分使用硬件来实现,哪一部分使用软件来实现,从而达到性能和功耗最佳平衡

- 使用低功耗软件

- 选择合适的处理器

2.2体系结构级降低功耗技术:

- 多电压设计技术(Multi-VDD):

包括电压控制单元:

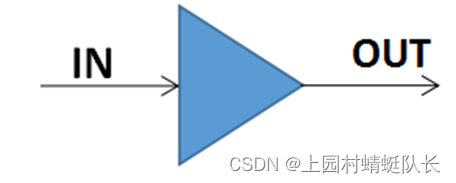

电平转换器(level shifter):把高(低)电压区域的信号转换到低(高)电压区域。信号通常包括数据、时钟、扫描链数据等。电平转换器的示意图如下所:

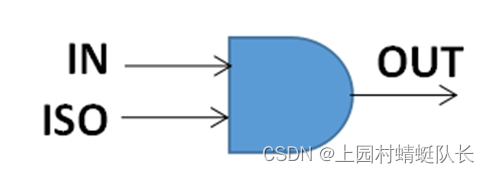

电源隔离单元(power isolation cell):主要用于模块的输入、输出。它可以关掉电源时,将信号保持为常数,从而避免单元的输入悬空。电源隔离单元如下图所示:

保持寄存器(retention register):在不工作的情况下,将寄存器的状态保留下来。

- 高级门控时钟Clock Gating: 使用时序门控时钟

- 动态电压频率调节(DVFS技术):降低时钟速率和供电电压

- 基于缓存的系统体系结构: 使用小范围的缓存

- 对数FFT体系结构: 基于对数系统实现FFT

- 异步(无时钟)设计: 移除时钟

- 电源门控Power Gating:(静态功耗)指芯片中某个区域的供电电源被关掉,即该区域内的逻辑电路的供电电源断开(在模块不使用时将其关闭),为了最小化漏电流,门控电源晶体常使用高阀值电压单元;

- 高阀值电压HVT:提高阈值电压,可以减小漏电流;

- 存储器电源门控:在不使用存储器时将其关闭(静态功耗)

2.3 RTL级降低功耗:

- 并行与流水:采用并行处理,可以降低系统工作频率,从而可能降低功耗.

- 状态机编码和解码:格雷码最适合低功耗设计,格雷码比用二进制码翻转更少,可以降低开关活动,功耗更低。

- 门控时钟:

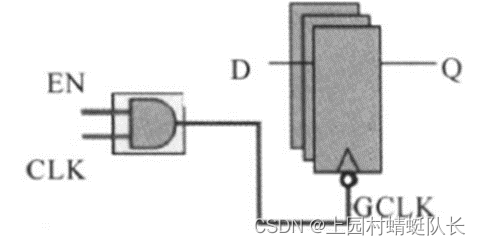

上述电路图中,将控制信号(EN)直接与时钟信号(CLK)进行与操作,以完成门控。门控后的时钟信号GCLK送到寄存器中,当EN为0时,该时钟被关掉。

低功耗题目

1.下列功耗措施哪个可以降低峰值功耗 D

A 静态模块级Clock Gating

B Memory Shut Down

C Power Gating

D 大幅度提高HVT比例

解析:首先峰值功耗是属于动态功耗中的短路功耗,即NMOS和PMOS同时导通所引起的峰值电流,最终带来的功耗。这个功耗和电源电压,时钟翻转率,以及峰值电流有关。

A选项静态门控时钟,所以A选项不正确。

B选项存储关闭。即不被访问的时候,关闭存储器,因而也是降低静态功耗。

C选项电源门控技术,即模块不工作的时候,关闭电源,模块睡眠,工作时候再启动电源,是降低静态功耗。

D选项即采用高阈值电压的晶体管,阈值电压增加的效果在于降低亚阈值漏电电流,并且短 路 功 耗 公 式 为 :Pshort = τAshortVdd = τAβ(Vdd-Vth)3 , 只 跟 Vth 有 关 , 而 D 选 项 中 大 幅 提 高 HVT ( High Voltage Value)带入短路功耗公式中会使短路功耗变小,从而降低动态功耗中的峰值功耗。所以D选项正确。

2.逻辑电路低功耗设计中,无效的方法是 A

A 采用慢速设计

B 减少信号翻转

C 采用较慢速的时钟

D 提高阈值电压

解析:A选项说采用慢速设计并不一定会降低功耗,所以A选项不正确。

B选项减少信号翻转可以降低动态功耗。

C选项采用较慢速时钟也相对的降低了信号的翻转,所以也是降低动态功耗。

D选项即采用高阈值电压的晶体管,阈值电压增加的效果在于降低亚阈值漏电电流,因而降低静态功耗。

3.在RTL设计阶段,降低功耗的常用设计方法是 B

A 门级电路的功耗优化

B 门控时钟

C 降低电路漏电流

D 多阈值电压

解析:这四个选项都是可以降低功耗的常用设计方法,但是有个前提,那就是在RTL设计阶段,也就是我们编写代码时可以控制的阶段,可以在代码中加入门控时钟,所以B选项正确。

4.某个状态下,不关心某个寄存器的输出值,那么将其设计为输出0,可以降低功耗(错误)

解析:比起设计为输出0,降低功耗更好的做法是保持寄存器原值。因为功耗来自于信号toggle,如果在上一状态寄存器输出为1,下一状态下输出为0,即便0不使用,也产生了0到1的跳变,同样会有功耗,既然不关心,还不如保持输出为1。

5.isolation cell是下面哪种低功耗技术必须的 B

A.Clk gating

B.Multi VDD

C.power gating

D.Multi VT

解析:如上介绍

6.以下哪个不是影响芯片功耗的基本要素:

电压 温度 工艺 湿度

7. 下列哪项不属于动态功耗? (C)

A.电路短路功耗

B.电路翻转功耗

C.二极管反向电流引起的功耗。

8. 以下哪几种因素会影响芯片的静态功耗(ACE)

A.工作电压

B.负载电容

C.工作温度

D.翻转活动因子

E.工艺

(时序分析)17.某条时序路径的保持时间不满足,可通过降低工作频率来满足保持时间(B)。

A.正确

B.错误

当保持时间不满足时理论上,可以增加Tffpd和Tcomb来解决,也就是增加触发器的D端到Q端的延时,以及两级触发器之间的组合逻辑电路部分。

目前大部分芯片的Thold时间都可以做到0ns。所以当保持时间不满足时,通常采用的做法是在传输路径上插入buffer,在不影响逻辑功能前提下,只具有增加延迟的作用。

PS:保持时间Thold和时钟频率之间是没有关系,故降低时钟速度不能解决保持时间不满足的问题,很多面试题喜欢在这里挖坑。

(时序分析)18. 格雷码的异步处理可以采用直接打拍的方式,在STA时不需要特殊检查(A)

A.正确

B.错误

STA只适用于同步电路

(SV)19. systemverilog中类默认的成员属性是(B)

A.private

B.public

C.automatic

D.local

另外两个分别是protected,local。需注意,public不是关键词。

(verilog)20. 下面哪些语句是不可综合的(CDE)

A.generate

B.always

C.time

D.initial

E.delays

(复位)21.在IC设计中,复位设计面临的主要问题包括(ABD)

A.时钟域的同步

B.去毛刺

C.可否做STA检查

D.对时钟的依赖程度

异步复位无法做STA检查

(verilog)22.下面关于always语句的使用描述正确的是(ABC)

A.在组合always模块中使用阻塞赋值语句

B.在时序always模块中使用非阻塞赋值语句

C.避免在组合always模块中敏感信号列表中缺少信号

D.避免敏感信号列表中出现冗余信号

(跨时钟)23.125MHz时钟域的多bit信号A[127:0]需要同步到25MHz时钟域,可能使用的同步方式有(ABD)

A.双向握手

B.DMUX

C.打三拍

D.异步FIFO

快到慢,多bit。

(亚稳态)24. 某个时钟域的建立时间要求是3ns,保持时间要求是3ns,那么如下几个寄存器,存在时序收敛问题的是:ACD

A.数据在一个时钟周期内的连续稳定时间为6ns,且数据在触发器时钟有效沿前,保持稳定不变的时间为4ns,

B.数据在一个时钟周期内的连续稳定时间为8ns,且数据在触发器时钟有效沿前,保持稳定不变的时间为4ns,

C.数据在一个时钟周期内的连续稳定时间为8ns,且数据在触发器时钟有效治前,保持稳定不变的时间为2ns,

D.数据在一个时钟周期内的连续稳定时间为6ns,且数据在触发器时钟有效沿前,保持稳定不变的时间的2ns,

setup hold ACD均不满足时序要求

A 4 2

B 4 4

C 2 6

D 2 4

亚稳态:34个题FPGA中亚稳态、异步信号处理、建立和保持时间违例及题目合集_Fighting_XH的博客-CSDN博客_静态配置信号可以不做异步处理

(亚稳态)25. 亚稳态对电路影响极大,下面哪种做法对降低亚稳态发生概率是无效的(C)

A增加异步处理的打拍级数

B使用专用亚稳态寄存器进行替换异步处理逻辑

C.提高异步处理电路的工作时钟

D.缩短异步处理打拍逻辑之间的delay

(FPGA)26. 对于FPGA内部的RAM而言,以下哪个说法是错误的?(A)

A配置成伪双端口RAM时,两个端口均有各自独立的读写控制信号

B.配置成伪双端口RAM时,两个端口,可以使用不同的时钟

C.配置成单端口RAM时,仅有一个时钟,用于读操作和写操作

D.配置成单端口RAM时,仅有一组访问地址,用于读操作或写操作

FPGA中的RAM有单端口、双端口和伪双端口之分.

单端口:

输入只有一组数据线和一组地址线,只有一个时钟,读写共用地址线。

输出只有一个端口。

所以单端口RAM的读写操作不能同时进行。

伪双端口:

输入有一组数据线,两组地址线,两个时钟。

两个输出端口共用一个输出端口。

所以一个端口只读,另一个端口只写,但写入和读取的时钟可以不同,且位宽比可以不是1:1。即允许写A的同时读B,且速率可以不同。

双端口:

输入有两组地址线和两组数据线,两个时钟。

输出有两个分别的数据线。

所以双口RAM两个端口都分别带有读写端口,可以在没有干扰的情况下进行读写,彼此互不干扰。

(verilog)27.状态机没有冗余状态时,可以不写default状态。(B)

A.正确

B.错误

状态机如果状态未列全,不需要使用default状态。(B)

A.正确

B.错误

状态机复位之后每个时刻都会处于某个状态。如果one-hot或者binary状态没用满,甚至就算用满了,也需要有一个default状态,用来保证预期之外的错误状态转移(比如亚稳态,glitch)时,能够回到一个稳定的已知状态,减小该预期之外的事件对数据通路造成影响的概率。

(低功耗)28. 下列关于实现不符合低功耗设计规范要求的是(C)

A.在不进行算术、逻辑运算的时候,使这些模块的输入保持“0”,不让操作数进来,输出结果不会翻转;而如果进行这方面的运算时,再将它们打开

B.FPGA全功能版本在产品适用温度范围内,结温不超过阀值的90%

C.接口电平如果可选,选择高电平模式

D.在满足性能要求时,尽量采用低的系统时钟

接口电平选择低电平模式,降低功耗,而且稳定;

(verilog)29. [多选题]下列说法正确的是(AD)

A.在always语句中赋值的变量,可以是wire也可以是reg

B.reg变量一定被综合为寄存器

C.always块只能用来描述组合逻辑

D.在assign语句中赋值的变量要定义为wire

实际上, reg 变量并不一定会被综合为寄存器( register ),之所以定义成 reg 类型,是表示从仿真的语义上来讲需要一个存储单元,而与综合后的硬件电路没有直接的关联,所以对初学者而言有时会具有误导性。是否有触发器,取决于时钟沿触发。

(verilog)30. 哪些情况下不会产生latch电路?(C)

A.使用if选择语句的组合逻辑没有else部分表达;

B.使用case选择语句的组合逻辑没有else表达

C.时序逻辑中if选择语句,没有else部分表达。

D.组合逻辑中条件不全的case语句没有default赋值;

(verilog)31. [单选题]关于verilog代码风格,以下说法错误的有:(C)

A.每个文件只能定义一个模块

B.Verilog区分大小写,所有信号命名能以大小写来区分不同信号

C.多个reg变量赋值,如果赋值条件完全相同,可以放在同一个always块内

D.每行只能有一个Verilog语句

32. 下列不属于异步时序电路设计特征的是:(A)

A.容易组织流水,提升芯片速率

B.不利于时序分析

C.依赖逻辑时延,时延不好控制

D.容易产生毛刺

33. 以下哪一项对于提高系统处理能力没有帮助(B)

A.减少寄存器翻转率

B.扩大数据位宽

C.缩短处理流水

D.提升系统工作频率

在进行数字信号处理的过程中,数据的宽度是非常非常关键的一点。在FPGA中实现的系统,数据每多一位,都意味着消耗了更多的资源。那么,一个优秀的系统,应该尽可能的在保证正确的前提下,减少数据的宽度..

34.同步电路设计中出现setup time不满足、不可以采用下面哪种措施解决(C)

A.降低时钟频率

B.pipeline

C.增加时钟频率

D.减小信号延迟

(verilog)35.initial语句,说法错误的是:(C)

A.在模拟的0时刻开始执行;

B.这是一种过程结构语句

C.可用于给实际电路赋初值

D.在仿真过程中只执行一次;

initial不可综合,无法给实际电路赋初值

36.异步时钟数据采样的方法错误的是(C)

A.使用fifo隔离进行多bit的采样;

B.握手信号后再采样;

C.高频时钟直接采样低频时钟的多bit数据;

D.单bit高频时钟脉冲展宽后给低频时钟进行采样

37.Verilog语言的层次高低对应(D)

A.系统级,行为级,功能级,寄存器传输级,门级

B.系统级,行为级,寄存器传输级,功能级,门级

C.系统级,功能级,寄存器传输级,行为级,门级

D.系统级,功能级,行为级,寄存器传输级,门级

38.设计异步FIFO时,FIFO深度必须是2的整数次幕,才能使用格雷码(A)

A.正确

B.错误

36.[单选题]模块端口的输入信号,如果没有进行赋值,其值是(C)。

A.1 B.C C.Z D.0

37.[单选题]基于Verilog HDL,时钟或复位信号可以出现在赋值表达式中。(A)

A.正确

B.错误

38.线型信号必须显示定义(B)

A.正确

B.错误

Verilog程序模块中输入、输出信号类型默认自动定义为wire型,可以不用显式定义

38.常说的7nm工艺,7nm指的是晶体管的(B)

A.漏极宽度

B.栅极宽度

C.整体宽度

D.源极宽度

39.竞争冒险现象怎样可以消除(ABD)

A.加入滤波电容

B.引入同步机制

C.不加选通信号

D.增加冗余逻辑

40.超大规模集成电路设计中,为了高速设计,采取以下哪些措施(AB)

A.流水线设计

B并行化设计

C.资源共享

D.串行化设计

高速设计要求并行化和流水线设计,牺牲集成电路面积,牺牲功耗。资源共享是降功耗

41.请找出以下总线中的串行总线(CD)

A.AXI

B.SDIO

C.UART

D.IIC

串行总线:SPI、I2C、UART

42. 以下verilog变量名合法的是(D)

A. 3sum

B. a/b

C. ab@cd

D. subSme_

verilog标识符支持数字、字母、$、_的组合,但是首字符必须是字母或下划线

43. D触发器:Tsetup=3ns,Thold=1ns,Tck2q=1ns,该D触发器最大可运行时钟频率是(D)

A、1GHZ

B、500MHZ

C、250MHZ

D、200MHZ

Tclk >= Tsetup + Tck2q = 4 ns;所以最大运行时钟250 MHz。

Thold与时钟的最大频率无关。

44. 关于代码覆盖率,描述正确的是(B)

A、代码覆盖率不包括toggle覆盖率

B、代码覆盖率包括line覆盖率

C、代码覆盖率包括功能覆盖率

D、代码覆盖率达到100%,表示验证足够完备,可以停止验证

代码覆盖率用于衡量你执行了多少设计代码,关注点在设计代码上,而不是测试平台,包括:

行覆盖率:多少行代码被执行过

路径覆盖率:在穿过代码和表达式的路径中有哪些已经被执行过

翻转覆盖率:哪些单位比特变量的值为0或1

状态机覆盖率:状态机哪些状态和状态转换已经被访问过

45. 以下不能对多bit的数据总线的时钟异步处理的是(B)

A、Gray-code

B、寄存器同步

C、FIFO

D、Dmux synchronizer

寄存器同步只适用于单bit信号

46. 在静态时序分析中计算时钟延迟需要考虑以下哪些因素(ACD)

A、时钟源的抖动(jitter)

B、寄存器的建立和保持时间

C、时钟树不平衡引入的偏差(skew)

D、工艺特性造成的on-chip variation

47.如下verilog描述中哪个或者哪几个会生成寄存器(BC)

A、always@(clk)

reg_a<=reg_b;

B、always@(negedge clk)

reg_a<= reg_b;

C、always@(posedge clk)

reg_a<=reg_b;

D、assign reg_a=reg_b;

B,C时钟边沿触发,D是组合逻辑。

48.对改善亚稳态问题有效果的方法是(ABCD)

A、引入同步机制,如加两级触发器

B、降低时钟频率

C、改善时钟质量,用边沿变化快速的时钟信号

D、用反应更快速的DFF

(verilog)49.线网类型变量未赋值,缺省值为Z。寄存器类型变量未赋值,缺省值为X。

(Verilog)50.

函数主要有一下特点:

①:不含有任何延迟,时序或时序控制逻辑。

②:至少有一个输入变量。

③:只有一个返回值,且没有输出。

④:不含有非阻塞语句。

⑤:函数可以调用其他函数,但不能调用任务;任务可以调用函数。

51. 目前主流的FPGA芯片仍是基于查找表。FPGA芯片主要由以下6部分组成。

①:可编程输入输出单元(IOB)

②:基本可编程逻辑单元(CLB)

③:完整的时钟管理模块

④:可编程连线资源

⑤:嵌入式块RAM

⑥:内嵌的底层功能单元和嵌入式专用硬核

52.

时序优化手段:

寄存器配平、

流水线设计、

关键路径优化。

面积优化手段:

逻辑优化、

资源共享、

串行化。

53. Xilinx的7系列FPGA内部有CLB可编程配置块,每个CLB里面有两个Slice. Slice有两种

SliceL:(Logic逻辑),SilceM:(Memory存储)。SliceM 相比 SliceL 多出的功能在于可以配置成 Distribute RAM(分布式RAM)。

SliceM 相比 SliceL 多了做存储器和移位的功能。

SliceM 相比 SliceL 中含有能够把LUT资源重新整合为RAM和ROM的逻辑。

54.奇校验:

原始码流 + 校验位 总共有奇数个1

偶校验:

原始码流 + 校验位 总共有偶数个1

55.全加器包括:

A.加数

B.进位输入

C.被加数

D.进位输出

E.加和输出

56.流水线设计的优点

A. 综合后电路的面积可以更小

B. 综合后电路的时钟频率可以更高

C. 综合欧电路的复杂性更低

D. 综合后的功耗更低

解:PIEPLINE的实际就是将串行操作变成并行操作,这样可以提高吞吐率提高时钟频率,

改善时序,但同时会导致数据延时,功耗增加,面积可能会增大(可能),设计变复杂.

57.使用相同时钟沿的同步数字电路,以下因素和最高工作频率无关的是()

A. 逻辑块间互联布线长度

B. 触发器的建立/保持时间

C. D触发器之间最长的组合逻辑

D. 时钟电平持续时间

解:

同步数字电路的最高频率主要取决于关键路径是否能够收敛,

与逻辑块之间的布线长度,触发器建立/保持时间

和D触发器之间最长的组合逻辑都有关。

但是时钟的低电平持续时间主要影响到时钟信号的有效性。

58.

ECC是一种能够实现“错误检查和纠正”的技术,有以下特性

1、只能修复1比特错误。能检测2比特错误。

当数据只有单比特错误时,ECC能够进行错误修复;超过2比特的数据错误,将无法修复,ECC只能输出多比特错误信号。

2、不保证能检测超过2比特的错误。

超过2比特的错误不一定能检测出来。

59.下面关于异步设计,正确的是(ACD)

A. 异步设计容易产生毛刺

B. 异步设计会带来很大的同步翻转噪声

C. 异步设计不能做时序约束,又不能做时序分析

D. 信号的时延随着每次布局线的不同而不同,随着PVT的改变而改变,因此可靠性很差,而且不容易移植

60.采用同步设计的好处(ABCD)

A. 避免器件受温度,电压,工艺的影响,易于节省功耗,易于消除毛刺

B. 整个电路有一个确定的初始态,且相对于异步逻辑节省实现面积

C. 易于运用流水线设计法

D. 便于运用静态时序分析等先进的设计工具

解:

---

同步设计能有效避免毛刺的影响,使得设计更加可靠。

毛刺是逻辑设计的天敌,毛刺使得数据变得混乱,可能引起电路功能的误判断。

当毛刺引入于时钟端或者异步复位端,就极有可能引起触发器的误翻转或者出现不正常的复位。

但是毛刺是与生俱来的,也就是说毛刺是不可避免的,一般来讲凡是有组合逻辑的地方肯定就有毛刺。同步设计是避免毛刺的最简单有效的方法。

---

同步设计可以减少环境对芯片的影响

由于芯片的实际工作环境比我们在测试的实验室环境恶劣的多,加之长时间运行,

随着芯片的温度的升高,电压的不稳定,将会使得器件内部时延发送变化,如果不使用同步设计的话,

对于时序要求比较苛刻的电路将无法正常工作。因为只有满足芯片的Static timing 的要求,才能保证芯片在预知的过程中工作。

---

同步设计可借助与STA工具进行时序分析,有助于提高设计的可靠性。

---

同步电路比较容易使用寄存器的异步复位/置位端,以使整个电路有一个确定的初始状。

---

同步电路可以很容易地组织流水线,提高芯片的运行速度,设计容易实现。

61.下面关于SRAM和DRAM的描述,正确的是(D)

A. DRAM比SRAM速度快

B. DRAM不需要刷新,SRAM需要刷新

C. DRAM比SRAM成本高

D. DRAM存储单元的结构比SRAM简单

解:

---

RAM随机存储器

存储单元的内容可按需随意取出或存入,且存取的速度与存储单元位置无关的存储器。这种存储器在 断电时将丢失其存储的内容 , 故主要用于存储段时间使用的程序。

---

SRAM(Static Random-Access Memory)

静态随机存取存储器: 只要供电它就会保持一个值。一般而言SRAM要比DRAM快,这是因为SRAM没有刷新周期。每个SRAM存储单元由6个晶体管组成,而DRAM存储单元由一个晶体管和一个电容器组成。相比而言,DRAM比SRAM每个存储单元的成本要高。照此推理,可以断定在给定的固定区域内DRAM的密度比SRAM 的密度要大。

---

DRAM (Dynamic Random Access Memory)

动态随机存取存储器: 这是一种以电荷形式进行存储的半导体存储器。DRAM中的每个存储单元由一个晶体管和一个电容器组成。数据存储在电容器中。电容器会由于漏电而导致电荷丢失,因而DRAM器件是不稳定的。为了将数据保存在存储器中,DRAM器件必须有规律地进行刷新。

---

SRAM常常用于高速缓冲存储器,因为它有更高的速率;而DRAM常常用于PC中的主存储器,因为其拥有更高的密度。

---

SDRAM(synchronous dynamic random-access memory)

同步动态随机存储器:意思是指理论上其速度可达到与CPU同步。

---

DDR SDRAM(Dual Date Rate SDRAM)

简称DDR,也就是“双倍速率SDRAM“的意思。DDR可以说是SDRAM的升级版本,DDR在时钟信号上升沿与下降沿各传输一次数据,这使得DDR的数据传输速度为传统SDRAM的两倍。

- 程序开发学习排行

- 最近发表